반도체 현존 최고 기술 ‘3나노’ 양산 돌입…차세대 기술도 준비

현재까지 시장의 판도는 과거와 다르지 않다. 여전히 TSMC가 우위에 있다. 애플 등 굵직한 기업들을 고객사로 확보했다는 사실이 알려졌다. 양산은 늦었지만 TSMC가 수율(전체 제품 가운데 결함이 없는 합격품 비율) 면에서 삼성전자를 앞설 것이라는 전망이 나오는 배경이다.

일각에서는 3나노 시장에서도 삼성전자가 TSMC를 따라잡기 쉽지 않을 것으로 예측한다. 삼성전자가 2015년 이후부터 파운드리 사업에 공격적으로 나섰지만 TSMC와의 점유율 격차가 좁혀지지 않고 있기 때문이다. 주요 기업들이 기존 거래처인 TSMC를 택한 결과다.

다만 이번에는 다를 수 있다는 전망이 나온다. 3나노 시장의 주도권을 뺏기지 않겠다는 삼성전자의 의지는 강력하다. 게이트 올 어라운드(GAA) 등 새로운 기술을 선제적으로 도입하고 이 기술을 단기간 내 안정화해 2024년까지 한 단계 업그레이드한 ‘2세대 3나노’를 시장에 내놓으며 TSMC를 추격할 계획이다.

◆ 삼성, ‘미세화·효율성’ 다 잡은 GAA 3나노 양산

파운드리는 회로 설계를 자체적으로 하지 않는 기업이 위탁하는 제품을 생산력이 있는 반도체 회사가 대신 생산해 주는 것을 의미한다. 파운드리 시장 규모가 커지면서 삼성전자와 TSMC 등 시장을 선도하는 반도체 기업들이 사업을 적극적으로 확대하는 추세다. 반도체 시장 조사 업체 IC인사이츠에 따르면 올해 글로벌 파운드리 시장 규모는 1321억 달러(약 179조원)로, 지난해보다 20% 커질 것으로 보인다.

삼성전자와 TSMC는 현재 ‘3나노(nm, 1nm는 10억분의 1m) 파운드리’ 시장을 놓고 선점 경쟁을 벌이고 있다. 양산은 삼성전자가 먼저 시작했지만 TSMC가 첫 고객으로 글로벌 스마트폰 기업 ‘애플’을 확보하면서 초미세 주도권을 확보하기 위한 이들의 힘 겨루기는 ‘현재 진행형’이다.

3나노 공정은 반도체 제조 공정 가운데 가장 앞선 기술이다. 반도체업계는 반도체 칩 회로 선폭의 기준을 나노미터 단위로 분류하는데 통상 5나노 이하 기술을 ‘초미세 공정’이라고 일컫는다. 나노의 크기를 줄이면 더 많은 웨이퍼를 생산할 수 있다는 장점이 있고 앞선 기술력을 통해 시장에서 우위를 점할 수 있어 글로벌 반도체 기업들이 선진화한 기술을 개발하기 위해 나서고 있다.

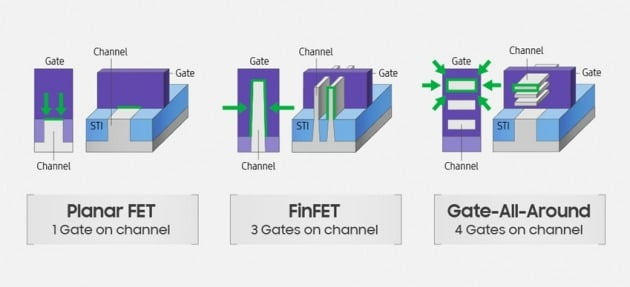

삼성전자는 지난 6월 세계 최초로 GAA 기술을 적용한 3나노 파운드리 공정 기반의 양산을 시작했다. GAA는 반도체를 구성하는 트랜지스터(반도체 소자)에서 전류가 흐르는 채널 4개면을 게이트가 둘러싸는 형태다.

삼성전자 3나노 GAA 1세대 공정은 기존 5나노 핀펫 공정과 비교해 전력을 45% 절감하고 성능을 23% 향상시켰다. 고성능 컴퓨팅(HPC)용 시스템 반도체를 초도 생산한 데 이어 모바일 시스템온칩(SoC) 등으로 확대해 나갈 예정이다.

삼성전자는 여기에 멈추지 않고 공정을 꾸준히 업그레이드해 2024년 3나노 GAA 2세대 공정을 계획하고 있다. 2세대 공정은 같은 기준으로 전력 50% 절감, 성능 30% 향상, 면적 35% 축소 등의 효과를 기대하고 있다.

삼성전자는 3나노 경쟁에서는 ‘해볼 만하다’고 판단하고 있다. 최시영 삼성전자 파운드리사업부장(사장)은 “삼성전자 파운드리는 하이케이 메탈 게이트(High-K Metal Gate), 핀펫(FinFET), 극자외선(EUV) 등 신기술을 선제적으로 도입하며 빠르게 성장해 왔다”며 “이번에 GAA 기술을 적용한 3나노 공정의 파운드리 서비스 또한 세계 최초로 제공하게 됐다. 앞으로도 차별화된 기술을 적극 개발하고 공정 성숙도를 빠르게 높이는 시스템을 구축해 나가겠다”고 강조했다.

◆ TSMC, 3나노 양산 예고…첫 고객으로 ‘애플’ 확보

하지만 대형 고객은 TSMC가 먼저 확보했다. 외신들은 TSMC가 9월 본격 양산에 돌입할 예정인 3나노 제품의 공급사로 애플을 확보했다는 소식을 전했다. TSMC가 단시간 내 공정 수율을 우수한 단계로 끌어올릴 가능성이 높다는 관측이 나오는 배경이다.

대만 정보기술(IT) 전문 매체 디지타임스는 “TSMC가 곧 3나노 공정 기술을 대량 생산 체제로 전환할 것”이라며 “첫 고객으로 애플을 확보하고 9월부터 3나노 칩 양산을 시작한다. 3나노 양산은 TSMC의 내년 상반기 매출에 크게 기여할 것으로 보인다”고 보도했다.

보도에 따르면 TMSC의 3나노 공정은 애플이 자체 설계한 M2 프로 칩에 적용될 것으로 예상된다. 애플은 M2 프로 칩을 탑재한 맥북 프로와 맥(PC) 미니 등을 이르면 연내 출시하기 위해 준비하고 있다.

디지타임스는 “삼성전자와 3나노 기술 경쟁을 벌이는 TSMC는 현재 애플·인텔·퀄컴·미디어텍·엔비디아·브로드컴·AMD 등 7개 글로벌 기업을 3나노 공정 고객으로 확보했다”고 덧붙였다.

업계에서는 고객사 확보를 ‘수율 개선’으로 보는 시각이 지배적이다. 수율은 쉽게 말해 그 공정에서 ‘불량률’을 얼마나 낮췄는지의 지표인데 초도 양산에선 수율이 가장 중요한 과제로 꼽힌다. 수율을 끌어올려야 생산성이 향상되고 수익성도 개선할 수 있다.

업계의 한 관계자는 “애플은 까다로운 고객사”라며 “그쪽에서 제시하는 기준은 매우 높다고 익히 알려져 있다. 공급사는 고객사가 제시한 기준을 만족시킬 능력이 있어야 하는데 애플이 TSMC의 3나노 공정을 채택했다는 것은 애플도 만족할 만큼의 수율이 나온다는 의미이기도 하다”고 설명했다.

현재 TSMC는 공식 홈페이지 내 기술 설명 카테고리에서 ‘TSMC의 3나노는 가장 진보한 파운드리 기술이 될 것’이라며 ‘기술 개발은 순조롭게 진행되고 있고 대량 생산은 올 하반기를 목표로 하고 있다. 우리의 3나노 공정은 5나노 대비 속도 15% 향상, 소비 전력 30% 감소 등의 효과가 난다’고 명시하고 있다.

1987년 설립된 TSMC가 파운드리 시장에서 삼성전자와 맞붙은 것은 2000년대 들어서다. 삼성전자는 2005년 시스템LSI사업부에서 파운드리 사업을 시작했기 때문이다. 비슷한 시기에 TSMC는 마이크로미터(㎛, 1㎛는 100만분의 1)에서 나노 단계로 기술을 업그레이드해 90나노 공정을 양산(2004년)했다.

이후 본격적인 미세화 경쟁이 시작됐다. TSMC가 후발 주자들을 견제하기 위해 90나노 양산 2년 만인 2006년에 65나노 양산까지 성공했고 삼성전자는 2007년과 2008년에 걸쳐 65나노, 55나노 제품 양산을 시작했다.

TSMC가 2008년 40나노까지 공정을 고도화하자 삼성전자는 이듬해 ‘로직공정연구소’를 신설하고 기술력 끌어올리기에 본격 착수했다. 그 결과 2011년 파운드리업계 최초로 32나노 하이케이메탈게이트(HKMG) 공정 양산에 성공했다.

삼성전자는 2014년 14나노 핀펫 공정 양산에 성공하며 비슷한 시기에 20나노 공정을 양산한 TSMC보다 앞선 기술력을 입증했다. 이후 삼성전자는 △2016년 10나노 핀펫 공정 양산 △2019년 EUV 기판 7나노 공정 양산 △2020년 5나노 공정 양산 △2021년 4나노 공정 양산 △2022년 3나노 공정 양산 등의 성과를 내며 TSMC를 맹추격하고 있다.

다만 여전히 시장을 선도하는 곳은 TSMC다. 대만 시장 조사 업체 트렌드포스에 따르면 파운드리 시장에서 TSMC의 글로벌 파운드리 시장점유율(매출 기준)은 올해 1분기 53.6%에 달한다. 삼성전자는 점유율 16.3%로 2위를 기록했지만 양 사의 격차는 여전히 크다.

삼성전자에 긍정적인 점은 양 사의 점유율 격차가 좁혀지고 있다는 점이다. 시장 조사 업체 IC인사이츠와 트렌드포스 등에 따르면 삼성전자의 파운드리 점유율은 2015년 5.3%에서 2017년 7.7%로 높아졌고 2018년 처음으로 두 자릿수(19.2%)의 점유율을 기록했다. 2015년 50% 이상 벌어진 점유율 격차를 3년 만에 30%포인트대 수준으로 좁혔고 이후 기술 개발과 양산에서도 TSMC를 앞서고 있다.

삼성전자의 목표는 파운드리 시장 1위다. 지난해 8월 ‘240조원 투자 계획’을 발표하면서 선단 공정 적기 개발과 과감한 투자를 통해 혁신 제품의 경쟁력을 확보해 글로벌 시스템 반도체(파운드리 등 비메모리) 시장에서 1위 기업으로 도약하겠다고 선언했다.

이 같은 삼성전자의 공격적 행보를 의식한 듯 TSMC 최고경영자(CEO)는 견제하는 듯한 발언을 하기도 했다. 웨이저자 CEO는 최근 타이베이에서 열린 연례 TSMC 기술 포럼 연설에서 “TSMC는 상품을 설계할 수 있는 능력이 있지만 절대 우리 제품을 만들지는 않는다”며 “고객은 TSMC에 설계를 빼앗길 걱정을 할 필요가 없다”고 말했다. 이어 “TSMC의 성공은 곧 고객의 성공이지만 경쟁 상대는 감히 이렇게 말할 수 없을 것”이라며 “고객이 성공하든 말든 경쟁 상대는 따로 자기 상품이 있다”고 덧붙였다. 스마트폰 등 완제품 사업을 함께하고 있는 삼성전자를 겨냥한 발언으로 업계는 해석하고 있다.

최수진 기자 jinny0618@hankyung.com

© 매거진한경, 무단전재 및 재배포 금지